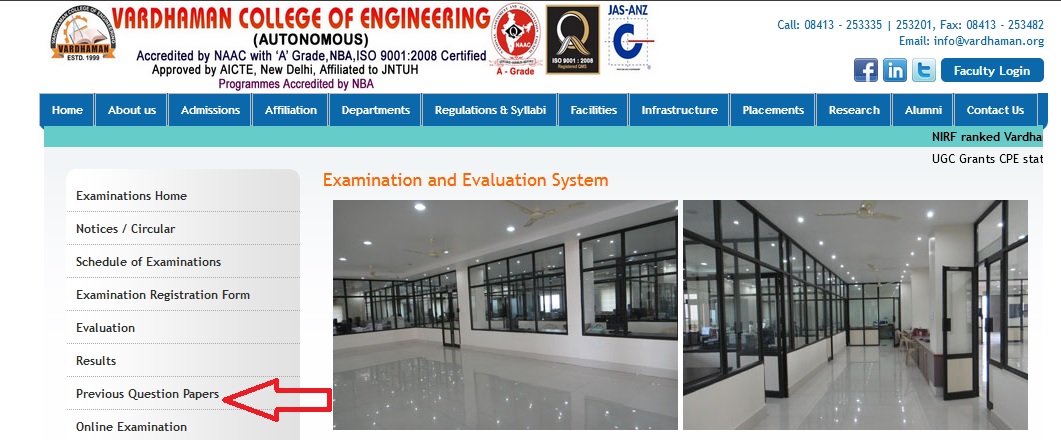

Digital Design Through Verilog Hdl B.Tech Question Paper : vardhaman.org

College : Vardhaman College Of Engineering

Degree : B.Tech

Department : Electronics & Communication Engineering

Semester : V

Subject : Digital Design Through Verilog Hdl

Document type : Question Paper

Website : vardhaman.org

Download Previous / Old Question Papers :

June – 2014 :https://www.pdfquestion.in/uploads/vardhaman.org/6375-BT5S%20JUNE14.pdf

December – 2013 : https://www.pdfquestion.in/uploads/vardhaman.org/6375-B.%20Tech%20V%20Semester%20Regular%20Examinations%20December%20-%202013.pdf

Vardhaman Digital Design Question Paper

Four Year B. Tech V Semester Supplementary Examinations June – 2014

(Regulations: VCE-R11)

(Electronics and Communication Engineering)

Date: 17 June, 2014 FN

Time: 3 hours

Max Marks: 75

Related / Similar Question Paper :

Vardhaman College B.Tech Integrated Circuits Applications Question Paper

Unit – I :

1. a) Briefly explain the steps involved in conventional electronic circuit design. 7M

b) Describe the following levels of design description: Circuit level, Gate level, Data flow, Behavioral level. 8M

2. a) Describe the physical design in a ASIC design flow. 7M

b) Explain the structure of a typical simulation module by using eight input NAND gate as an example? 8M

Unit – II :

3. a) With instantiation, functional representation and functional description, explain tri-state buffer primitives. 8M

b) Write Verilog module for 8-bit comparator with test bench. 7M

4. Explain in detail net, gate and tri-state delays with examples and Verilog code? 15M

Unit – III :

5. a) Design a module of an up-down counter and a test bench for the same. 7M

b) With an example explain how the INITIAL construct used in Verilog. 8M

6. a) Explain how the ALWAYS statements are used in Verilog? 8M

b) Design a counter module and test bench to illustrate the use of WAIT construct in a Verilog. 7M

Unit – IV :

7. a) Explain with example how assign and net declarations can be combined? 5M

b) Write the operator precedence for unary, binary and ternary operators in Verilog. 10M

8. a) Draw the basic functional unit of a dynamic shift register using switch level modelling. Also write Verilog module and test bench. 10M

b) Differentiate between regular and resistive switches in Verilog. 5M

Unit – V :

9. a) Illustrate the differences between *> and => operators in specify block. 8M

b) Why ‘specparam’ construct is used in specify block? Explain. Also compare ‘specparam’ and ‘parameter’. 7M

10. a) Explain recursive function with example? 6M

b) Briefly explain combinational and sequential UDPs in Verilog. Also write Verilog module for D latch using UDP. 9M

December – 2013

B. Tech V Semester Regular Examinations, :

Regulations: VCE-R11

Digital Design Through Verilog HDL :

(Electronics and Communication Engineering

Date : 10 December, 2013

Time : 3 Hours

Max. Marks : 75

Answer ONE question from each Unit

All Questions Carry Equal Marks

All parts of the question must be answered in one place only :

Unit – 1 :

1. a) What is the need for synthesis? Briefly discuss the two common approaches for hardware realization using synthesis tool. 5M

b) Discuss different levels of design description in Verilog with suitable examples. 10M

2. a) Discuss the different driving strengths in Verilog with strength level, keyword and element modeled. 12M

b) Write the structure of typical simulation module and explain. 3M

Unit – 2 :

3. a) For AOI gate write Verilog module and test bench module. 8M

b) Draw a 3-to-8 decoder using 2-to-4 decoder and write the Verilog module for the same. 7M

4. a) Draw the gate level circuit of edge-triggered flip-flop and write the Verilog module. 7M

b) Explain ‘wand’ and ‘wor’ types of nets with examples. 8M

Unit – 3 :

5. a) With an example explain the blocking and non-blocking assignments in Verilog. 8M

b) Design a module for 4-bit four functions ALU and also a test bench for the same by using behavioral modeling.7M

6. a) Design a module for a 2-bit priority encoder using the ‘casez’ statement and test bench for the same. 8M

b) Design a 2:4 demultiplexer module and test bench using the if-else-if construct in a Verilog. 7M

Unit – 4 :

7. a) Design BCD adder module and test bench using data flow level. 8M

b) Design a CMOS inverter formed by connecting NMOS and PMOS transistors in series. 7M

8. a) Write a Verilog design description module of a CMOS NOR gate. 8M

b) Design a module for a ring counter and write a test bench for the same. 7M

Unit – 5 :

9. a) With an example explain how ‘specparam’ statements used in Verilog. 8M

b) Write a module for parity generation through a ‘function’. 7M

10. a) With an example explain the use of path delay assignments in Verilog. 7M

b) Design a module for 32-bit adder with the addition done in successive clock pulses. 8M

This questions will come for all colleges or only autonomous?